# TINSHARP Industrial Co., Ltd.

# DATA SHEET

# LCM MODULE

# **TG12864-COG7D**

Specification for Approval

| APPROVED BY | CHECKED BY | PREPARED BY |

|-------------|------------|-------------|

| Casos       | Stofm      | 1836        |

ISSUED: V00 2013-11-26

# **CONTENTS**

| FUNCTIONS & FEATURES                                 | 3  |

|------------------------------------------------------|----|

| BLOCK DIAGRAM                                        | 3  |

| MODULE OUTLINE DRAWING                               | 4  |

| INTERFACE PIN FUNCTIONS                              | 5  |

| ABSOLUTE MAXIMUM RATINGS (Ta = 25 $^{\circ}$ )       | 6  |

| DC ELECTRICAL CHARACTERISTICS                        | 6  |

| LED BACKLIGHT CHARACTERISTICS                        | 6  |

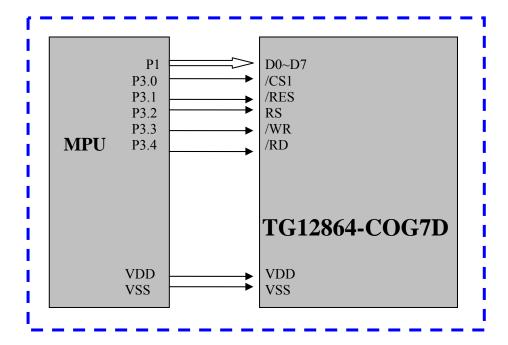

| CONNECTION WITH MCU                                  | 7  |

| Reference Power Supply Circuit for Driving LCD Panel | 7  |

| TIMING CHARACTERISTICS                               | 8  |

| OPTICAL CHARACTERISTICS                              | 12 |

| DISPLAY COMMANDS                                     | 13 |

| DISPLAY DATA RAM                                     | 15 |

| RESET CIRCUIT                                        | 20 |

| RELIABILITY TEST CONDITION                           | 21 |

| PRECAUTION FOR USING LCM MODULE                      | 22 |

| OTHERS                                               | 22 |

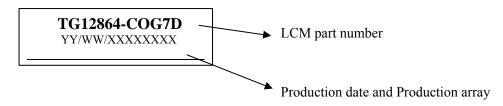

| APPENDIX A: DATE CODE RULES                          | 23 |

| APPENDIX B. CHANGE NOTES                             |    |

#### **FUNCTIONS & FEATURES**

• Construction : COG (Chip-on-Glass)

• Display Format : 128x64 dots

• Display Type : FSTN, Transmissive, Positive, B-W

• Controller : NT7538H or equivalent controller

Interface : 8-bit parallel interface

Backlight : White/side light

• Viewing Direction : 6 O'clock

• Driving Scheme : 1/65 Duty Cycle, 1/9 Bias

• Power Supply Voltage : 3.3 V

•  $V_{LCD}$  Adjustable For Best Contrast : 9.0 V ( $V_{OP}$ .) • Operation temperature : -10°C to +60°C

Storage temperature :  $-20^{\circ}$ C to  $+70^{\circ}$ C

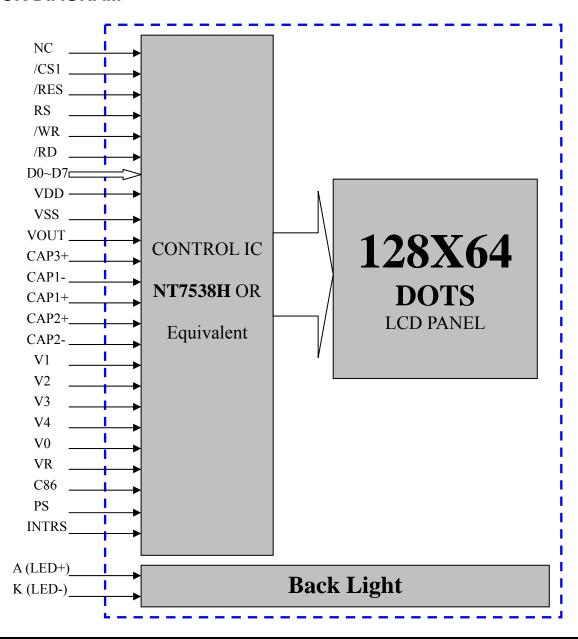

#### **BLOCK DIAGRAM**

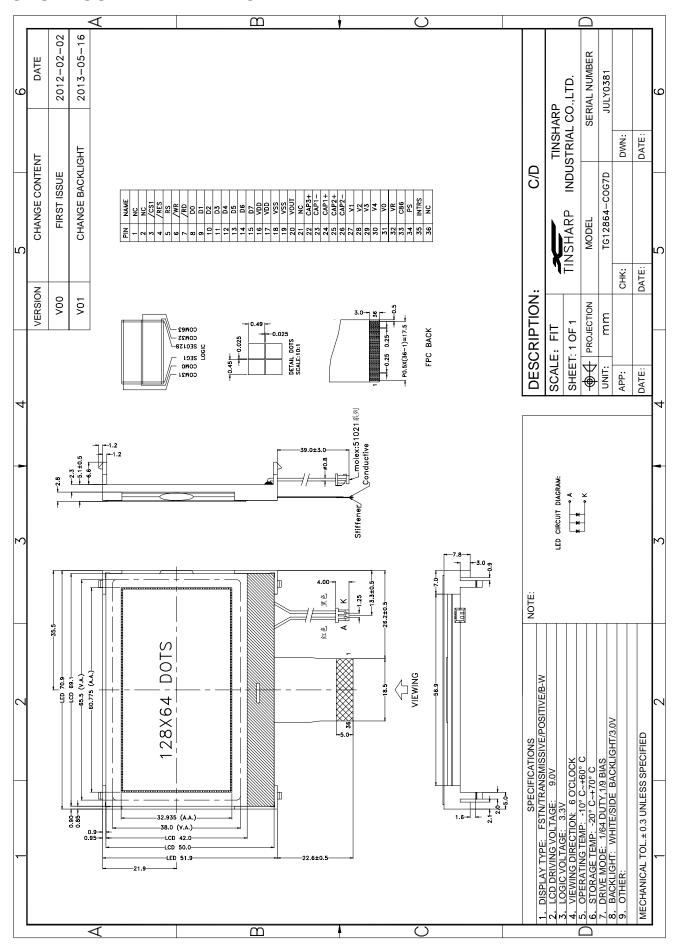

## **MODULE OUTLINE DRAWING:**

# **INTERFACE PIN FUNCTIONS:**

| Pin<br>No. | Symbol                                                                         | Level      | Description                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|------------|--------------------------------------------------------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 1          | NC                                                                             |            | Non-connection.                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| 2          | NC                                                                             |            | Non-connection.                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| 3          | /CS1                                                                           | H/L        | This is the chip select signal. When /CS1="L", then the chip select becomes active, and data /command I/O is enable.                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| 4          | /RES                                                                           | H/L        | When /RES is set to "L", the settings are initialized.                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| 5          | RS                                                                             | H/L        | This is connected to the least significant bit of the normal MPU address bus, and it determines whether the data bits are data or a command.  RS=L: D0 to D7 are control data.  RS=H: D0 to D7 are display data.                                                                                                          |  |  |  |  |  |  |  |

| 6          | /WR                                                                            | H/L        | When connected to an 8080 MPU, this is active LOW. This terminal connects to the 8080 MPU /WR signal. The signals on the data bus are latched at the rising edge of the /WR signal. When connected to a 6800 Series MPU, this is the read/write control signal input terminal. When R/W = "H": Read When R/W = "L": Write |  |  |  |  |  |  |  |

| 7          | /RD                                                                            | H/L        | When connected to an 8080 MPU, it is active LOW. This pad is connected to the /RD signal of the 8080MPU, and the NT7538 data bus is in an output status when this signal is "L". When connected to a 6800 Series MPU, this is active HIGH. This is used as an enable clock input of the 6800 series MPU.                  |  |  |  |  |  |  |  |

| 8          | D0                                                                             | H/L        |                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| 9          | D1                                                                             | H/L        | This is an 8-bit bi-directional data bus that connects to an 8-bit or 16-bit standard MPU data bus.                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| 10         | D2                                                                             | H/L        | When the serial interface is selected (P/S="L"), then D7 serves as the serial data input terminal                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| 11         | D3                                                                             | H/L        | (SI) and D6 serves as the serial clock input terminal (SCL). When the serial interface is selected,                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| 12         | D4                                                                             | H/L        | fix D0~D5 pads to VDD or VSS level.                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| 13         | D5                                                                             | H/L        | When the chip select is inactive, D0 to D7 are set to high impedance.                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| 14<br>15   | D6<br>D7                                                                       | H/L<br>H/L |                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| 16-17      | VDD                                                                            | +3.3V      | Supply voltage for logic operating.                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| 18-19      | VSS                                                                            | 0V         | Ground output for pad option.                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| 20         | VOUT                                                                           |            | DC/DC voltage converter output.                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| 21         | NC                                                                             |            | NC                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| 22         | CAP3+                                                                          | H/L        | DC/DC voltage converter. Connect a capacitor between this terminal and the C1- terminal.                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 23         | CAP1-                                                                          | H/L        | DC/DC voltage converter. Connect a capacitor between this terminal and the C1+ terminal.                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 24         | CAP1+                                                                          | H/L        | DC/DC voltage converter. Connect a capacitor between this terminal and the C1- terminal.                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 25         | CAP2+                                                                          | H/L        | DC/DC voltage converter. Connect a capacitor between this terminal and the C2- terminal.                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 26         | CAP2-                                                                          | H/L        | DC/DC voltage converter. Connect a capacitor between this terminal and the C2+ terminal.                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 27         | V1                                                                             | H/L        | LCD driver supplies voltages. The voltage determined by the LCD cell is impedance-converted by                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| 28         | V2                                                                             | H/L        | a resistive driver or an operation amplifier for application. Voltages should be according to the                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| 29         | V3                                                                             | H/L        | following relationship: $V0 \ge V1 \ge V2 \ge V3 \ge V4 \ge VSS2$ .                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| 30         | V4                                                                             | H/L        | When the on-chip operating power circuit is on, the following voltages are supplied to V1 to V4 by the on-chip power circuit. Voltage selection is performed by the LCD bias SET command.                                                                                                                                 |  |  |  |  |  |  |  |

|            |                                                                                |            | LCD bias V1 V2 V3 V4                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|            |                                                                                |            | 1/4 bias 3/4 V0 2/4 V0 1/4 V0                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|            |                                                                                |            | 1/5 bias 4/5 V0 3/5 V0 2/5 V0 1/5 V0                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| 31         | V0                                                                             | H/L        | 1/6 bias 5/6 V0 4/6 V0 2/6 V0 1/6 V0                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|            |                                                                                |            | 1/7 bias 6/7 V0 5/7 V0 2/7 V0 1/7 V0                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|            |                                                                                |            | 1/8 bias 7/8 V0 6/8 V0 2/8 V0 1/8 V0                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|            |                                                                                |            | 1/9 bias 8/9 V0 7/9 V0 2/9 V0 1/9 V0                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| 32         | VR                                                                             |            | Voltage adjustment pad. Applies voltage between V0 and VSS using a resistive divider.                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| 33         | C86                                                                            | H/L        | This is the MPU interface switch terminal C86 = "H": 6800 Series MPU interface                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|            |                                                                                |            | C86 = "L": 8080 Series MPU interface  This is the parallel data input/serial data input switch terminal  P/S = "H": Possible data input                                                                                                                                                                                   |  |  |  |  |  |  |  |

|            |                                                                                |            | P/S = "H": Parallel data input P/S = "L": Serial data input                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|            |                                                                                |            | The following applies depending on the P/S status:                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

|            |                                                                                |            | P/S Data/Command Data Read/Write Serial Clock                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| 34         | PS                                                                             | H/L        |                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|            |                                                                                |            | "H" A0 D0 to D7 /RD, /WR -                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|            |                                                                                |            | "L" A0 SI (D7) Write only SCL (D6)                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

|            |                                                                                |            | When P/S = "L", fix D0~D5 pads to VDD or VSS level. /RD (E) and /WR (R/W) are fixed to either                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|            | "H" or "L". With serial data input, RAM display data reading is not supported. |            |                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|            |        | _     |                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------|--------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>No. | Symbol | Level | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

| 35         | INTRS  | H/L   | This terminal selects the resistors for the V0 voltage level adjustment.  IRS = "H", Use the internal resistors  IRS = "L", Do not use the internal resistors  The V0 voltage level is regulated by an external resistive voltage divider attached to the VR terminal. This pad is enabled only when the master operation mode is selected. It is fixed to either "H" or "L" when the slave operation mode is selected. |

| 36         | NC     |       | Non-connection.                                                                                                                                                                                                                                                                                                                                                                                                         |

| Pin<br>No. | Symbol   | Level | Description                  |

|------------|----------|-------|------------------------------|

| 1          | A (LED+) | +3.0V | Power supply for Back Light. |

| 2          | K (LED-) | 0V    | Ground for Back Light.       |

# ABSOLUTE MAXIMUM RATINGS ( Ta = $25^{\circ}$ ):

| Parameter                    | Symbol      | Min  | Max                  | Unit       |

|------------------------------|-------------|------|----------------------|------------|

| Supply voltage for logic     | $V_{ m DD}$ | -0.3 | +4.0                 | V          |

| Supply voltage for LCD       | Vo          | -0.3 | +15.0                | V          |

| Input voltage                | Vı          | -0.3 | V <sub>DD</sub> +0.3 | V          |

| Normal Operating temperature | Тор         | -10  | +60                  | $^{\circ}$ |

| Normal Storage temperature   | Tst         | -20  | +70                  | $^{\circ}$ |

**Note:** Stresses beyond those given in the Absolute Maximum Rating table may cause operational errors or damage to the device. For normal operational conditions see AC/DC Electrical Characteristics.

## DC ELECTRICAL CHARACTERISTICS

| Parameter                     | Symbol | Condition | Min     | $T_{YP}$ | Max    | Unit |

|-------------------------------|--------|-----------|---------|----------|--------|------|

| Supply voltage for logic      | VDD    |           | 2.8     | 3.3      | 3.4    | V    |

| Supply current for logic      | IDD    |           |         | 2        | 5      | mA   |

|                               |        | -10℃      |         |          |        |      |

| Operating voltage for LCD     | VLCD   | +25°C     | 8.7     | 9.0      | 9.3    | V    |

|                               |        | +60°C     |         |          |        |      |

| Input voltage "H" level       | VIH    |           | 0.8 VDD |          | VDD    | V    |

| Input voltage "L" level       | VIL    |           | 0       |          | 0.2VDD | V    |

| Supply voltage for Back Light | VBL    |           | 2.8     | 3.0      | 3.2    | V    |

| Supply current for Back Light | IBL    |           | 35      | 45       | 55     | mA   |

• NOTES: parallel interface 8080 Series MPU

PS= "H"

INTRS= "H"

C86= "L"

parallel interface 6800 Series MPU

PS= "H"

INTRS= "H"

C86= "H"

Serial Interface PS= "L"

INTRS= "H"

C86= "H"

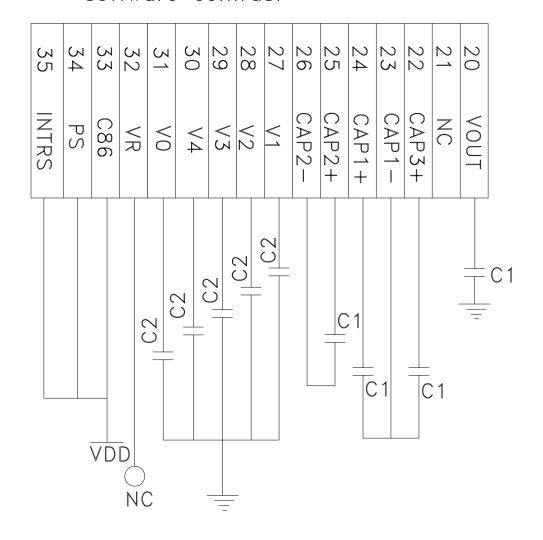

#### **Reference Power Supply Circuit for Driving LCD Panel**

6800 MPU PARALLEL NTERFACE

C1 C2:1UF/35V

Internal resistor

software contrast

#### **TIMING CHARACTERISTICS**

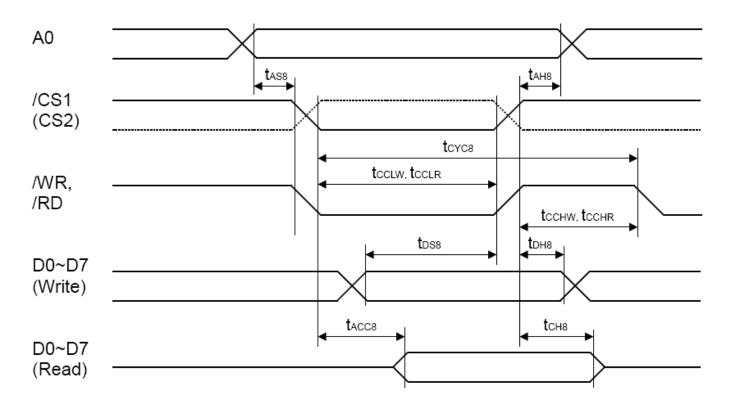

## 1. System Buses Read/Write Characteristics (for 8080 Series MPU)

|                  |                                  |      |      | (100 | 2.7  | 5.6 v, 1a - 16 · 66 6) |  |

|------------------|----------------------------------|------|------|------|------|------------------------|--|

| Symbol           | Parameter                        | Min. | Тур. | Max. | Unit | Condition              |  |

| Танв             | Address hold time                | 0    | -    | -    | ns   | 40                     |  |

| Tass             | Address setup time               | 0    | -    | -    | ns   | A0                     |  |

| tcycs            | System cycle time                | 240  | -    | -    | ns   |                        |  |

| tccLw            | Control low pulse width (write)  | 90   | -    | -    | ns   | /WR                    |  |

| tccLR            | Control low pulse width (read)   | 120  | -    | -    | ns   | /RD                    |  |

| tсснw            | Control high pulse width (write) | 100  | -    | -    | ns   | WR                     |  |

| tcchr            | Control high pulse width (read)  | 60   | -    | -    | ns   | /RD                    |  |

| T <sub>DS8</sub> | Data setup time                  | 40   | -    | -    | ns   | D0- D7                 |  |

| Тонв             | Data hold time                   | 0    | -    | -    | ns   | D0~D7                  |  |

| taccs            | /RD access time                  | -    | -    | 140  | ns   | D0-D7 CL = 100-F       |  |

| Тснв             | Output disable time              | 5    | -    | 50   | ns   | D0~D7, CL = 100pF      |  |

<sup>\*1.</sup> The input signal rise time and fall time  $(t_r, t_f)$  is specified at 15ns or less.  $(t_r + t_f) < (tcycs - tcclw - tcchw)$  for write,  $(t_r + t_f) < (tcycs - tcclr - tcchr)$  for read.

<sup>\*2.</sup> All timing is specified using 20% and 80% of VDD as the reference.

<sup>\*3.</sup> tccLw and tccLR are specified as the overlap interval when /CS1 is low (CS2 is high) and /WR or /RD is low.

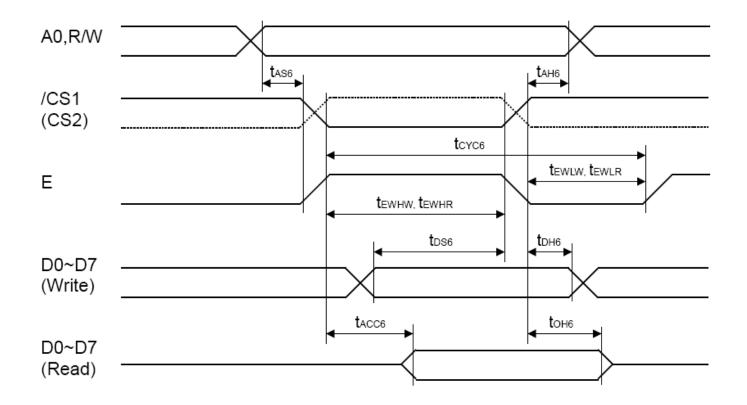

# 2. System Buses Read/Write Characteristics (for 6800 Series MPU)

$(VDD = 2.7 \sim 3.6V, Ta = -40 \sim +85^{\circ}C)$

|        | I                                |      |      | (۷00- | 2.7  | 3.6V, 1a = -40 ~ +85°C) |  |

|--------|----------------------------------|------|------|-------|------|-------------------------|--|

| Symbol | Parameter                        | Min. | Тур. | Max.  | Unit | Condition               |  |

| tah6   | Address hold time                | 0    | -    | -     | ns   | A0, R/W                 |  |

| tase   | Address setup time               | 0    | -    | -     | ns   | A0, N/VV                |  |

| tcyce  | System cycle time                | 240  | -    | -     | ns   |                         |  |

| tеwнw  | Control high pulse width (write) | 90   | -    | -     | ns   | Е                       |  |

| tewnr  | Control high pulse width (read)  | 120  | -    | -     | ns   | Е                       |  |

| tewLw  | Control low pulse width (write)  | 100  | -    | -     | ns   | E                       |  |

| tewLR  | Control low pulse width (read)   | 60   | -    | -     | ns   | E                       |  |

| tos6   | Data setup time                  | 40   | -    | -     | ns   | D0- D7                  |  |

| tоне   | Data hold time                   | 0    | -    | -     | ns   | D0~D7                   |  |

| tacc6  | /RD access time                  | -    | -    | 140   | ns   | D0~D7                   |  |

| tоне   | Output disable time              | 5    | -    | 50    | ns   | CL = 100pF              |  |

<sup>\*1.</sup> The input signal rise time and fall time  $(t_r, t_f)$  is specified at 15ns or less.  $(t_r + t_f) < (tcyc_6 - tewlw - tewhw)$  for write,  $(t_r + t_f) < (tcyc_6 - tewlw - tewhw)$  for read.

<sup>\*2.</sup> All timing is specified using 20% and 80% of VDD as the reference.

<sup>\*3.</sup> tewhw and tewhr are specified as the overlap interval when /CS1 is low (CS2 is high) and E is high.

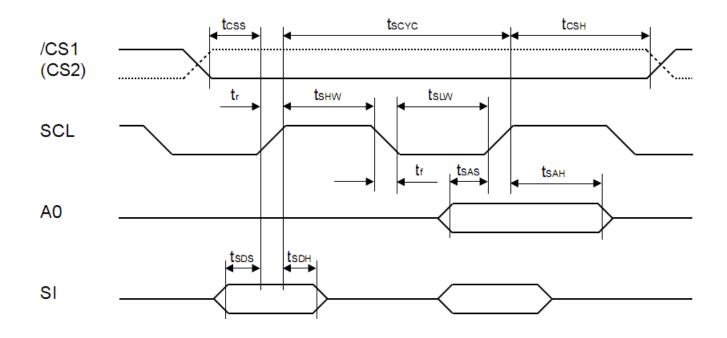

# 3. Serial Interface Timing:

$(VDD = 2.7 \sim 3.6V, Ta = -40 \sim +85^{\circ}C)$

| Symbol | Parameter                  | Min. | Тур. | Max. | Unit | Condition |

|--------|----------------------------|------|------|------|------|-----------|

| tscyc  | Serial clock cycle         | 120  | -    | -    | ns   | SCL       |

| tsнw   | Serial clock H pulse width | 60   | -    | -    | ns   | SCL       |

| tsLw   | Serial clock L pulse width | 60   | -    | -    | ns   | SCL       |

| tsas   | Address setup time         | 30   | -    | -    | ns   | A0        |

| tsah   | Address hold time          | 20   | -    | -    | ns   | A0        |

| tsps   | Data setup time            | 30   | -    | -    | ns   | SI        |

| tsрн   | Data hold time             | 20   | -    | -    | ns   | SI        |

| tcss   | Chip select setup time     | 20   | -    | -    | ns   | /CS1, CS2 |

| tсsн   | Chip select hold time      | 40   | -    | -    | ns   | /CS1, CS2 |

<sup>\*1.</sup> The input signal rise time and fall time (tr, tr) is specified as 15ns or less.

<sup>\*2.</sup> All timing is specified using 20% and 80% of VDD as the standard.

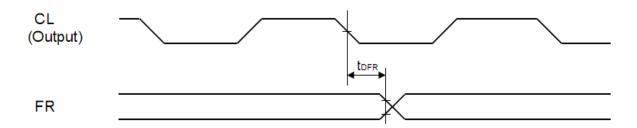

# **Display Control Timing:**

$(VDD = 2.7 \sim 3.6V, Ta = -40 \sim +85^{\circ}C)$

| Symbol | Parameter                      | Min. | Тур. | Max. | Unit | Condition  |

|--------|--------------------------------|------|------|------|------|------------|

| tofr   | t <sub>DFR</sub> FR delay time |      | 20   | 80   | ns   | CL = 50 pF |

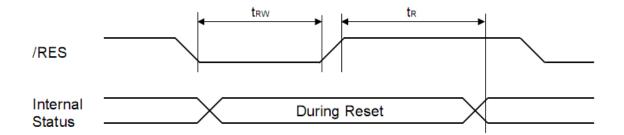

# **Reset Timing**

$(VDD = 2.7 \sim 3.6V, Ta = -40 \sim +85^{\circ}C)$

| Symbol | Parameter             | Min. | Тур. | Max. | Unit | Condition |

|--------|-----------------------|------|------|------|------|-----------|

| tr     | Reset Time            | -    | -    | 1.0  | μs   |           |

| trw    | Reset low pulse width | 10   | -    | -    | μs   | /RES      |

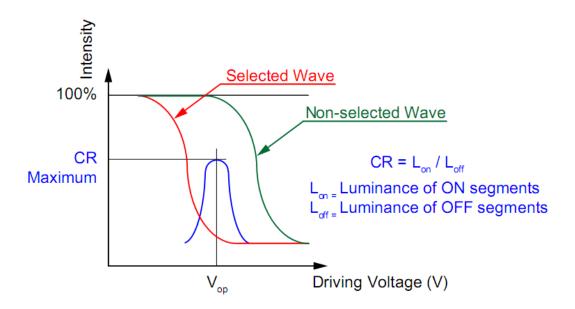

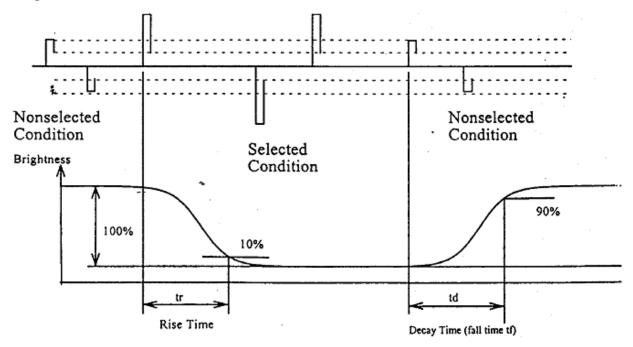

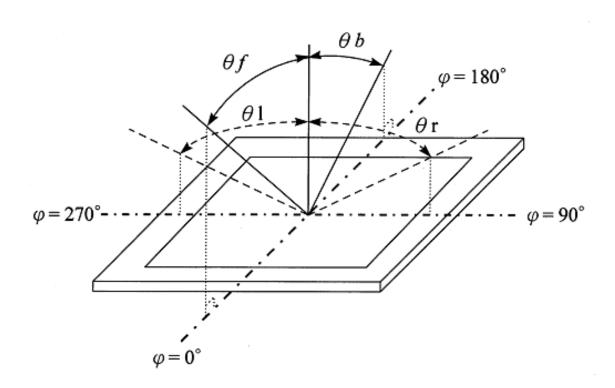

# **OPTICAL CHARACTERISTICS:**

| ITEM                | SYMBOL | CONDITION          | MIN | TYP | MAX | UNIT | NOTE |

|---------------------|--------|--------------------|-----|-----|-----|------|------|

| Contrast ratio      | CR     | $\theta=0, \Phi=0$ | 1   | 5   | -   |      |      |

| Response time(rise) | Tr     | 25℃                |     | -   | 250 | mg   |      |

| Response time(fall) | Td     | 25 C               |     | -   | 350 | ms   |      |

|                     | θf     |                    |     |     |     |      |      |

| Vioving angle       | θЬ     | 25.00              |     |     |     |      |      |

| Viewing angle       | θΙ     | 25℃                |     | -   |     | dag  |      |

|                     | θr     |                    |     | -   |     | deg. |      |

Note1: Definition Operation Voltage  $(V_{OP})$ .

**Note2: Response time**

**Note3: Viewing angle**

#### **DISPLAY COMMANDS**

Command

#### **Table of NT7538 Commands:**

Α0

0

0

0

1

1

1

0

0

0

/RD

/WR

D7

| (1) Display OFF            | 0 | 1 | 0 | 1 | 0   | 1          | 0    | 1       | 1       | 1             | 0                              | 1                               | Turn on LCD panel when high, and turn off when low                   |  |  |

|----------------------------|---|---|---|---|-----|------------|------|---------|---------|---------------|--------------------------------|---------------------------------|----------------------------------------------------------------------|--|--|

| (2) Display Start Line Set | 0 | 1 | 0 | 0 | 1   |            | Disp | lay Sta | art Add | dress         |                                | 40h<br>to<br>7Fh                |                                                                      |  |  |

| (3) Page Address Set       | 0 | 1 | 0 | 1 | 0   | 1          | 1    | F       | age A   | ddres         | S                              | B0h<br>to<br>B8h                | Set the display data RAM page in<br>Page Address register            |  |  |

| (4) Column Address Set     | 0 | 1 | 0 | 0 | 0   | 0          | 1    | Н       | •       | Colum<br>ress | ın                             | 00h<br>to                       | Set 4 higher bits and 4 lower bits of column address of display data |  |  |

| (4) Column Address Set     | 0 | 1 | 0 | 0 | 0   | 0          | 0    | L       |         | Colum<br>ress | n                              | 18h                             | RAM in register                                                      |  |  |

| (5) Read Status            | 0 | 0 | 1 |   | Sta | itus       |      | 0       | 0       | 0             | 0                              | XX                              | Reads the status information                                         |  |  |

| (6) Write Display Data     | 1 | 1 | 0 |   |     | Write Data |      |         |         | XX            | Write data in display data RAM |                                 |                                                                      |  |  |

| (7) Read Display Data      | 1 | 0 | 1 |   |     |            | Read | Data    | Data    |               | XX                             | Read data from display data RAM |                                                                      |  |  |

| (8) ADC Select             | 0 | 1 | 0 | 1 | 0   | 1          | 0    | 0       | 0       | 0             | 0                              | A0h                             | Set the display data RAM address                                     |  |  |

0

0

0

0

D4

D5

D6

0

0

0

1

1

1

1

1

Code

D3

D2

1

1

0

1

0

1

D1

Hex

D0

0

0

0

A2h

A3h

(9) Normal/Reverse Display

(10) Entire Display ON/OFF

11)LCD Bias Set

Sets LCD driving voltage bias ratio

A1h SEG output correspondence

A7h |full indication when high

A5h display on

A6h Normal indication when low, but

A4h Select normal display (0) or entire

(Note)\*: ignored data

**Function**

|                                                                                                                                                                                                                                                                                             |                   |                 |                            |                                 |               | $\overline{}$     |                       |                             |                                   |                                    |                         |                                                                                | <b>—</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|----------------------------|---------------------------------|---------------|-------------------|-----------------------|-----------------------------|-----------------------------------|------------------------------------|-------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| (12)Read-Modify-Write                                                                                                                                                                                                                                                                       | 0                 | 1               | 0                          | 1                               | 1             | 1                 | 0                     | 0                           | 0                                 | 0                                  | 0                       | E0h                                                                            | Increments column address counter during each write                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| (13)End                                                                                                                                                                                                                                                                                     | 0                 | 1               | 0                          | 1                               | 1             | 1                 | 0                     | 1                           | 1                                 | 1                                  | 0                       | EEh                                                                            | Releases the Read-Modify-Write                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| (14)Reset                                                                                                                                                                                                                                                                                   | 0                 | 1               | 0                          | 1                               | 1             | 1                 | 0                     | 0                           | 0                                 | 1                                  | 0                       | E2h                                                                            | Resets internal functions                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| (15)Common Output Mode<br>Select                                                                                                                                                                                                                                                            | 0                 | 1               | 0                          | 1                               | 1             | 0                 | 0                     | 0                           | *                                 | ٠                                  | *                       | C0h<br>to<br>CFh                                                               | Select COM output scan direction *: invalid data                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| (16)Power Control Set                                                                                                                                                                                                                                                                       | 0                 | 1               | 0                          | 0                               | 0             | 1                 | 0                     | 1                           | Opera                             | ation S                            | Status                  | 28h<br>to<br>2Fh                                                               | Select the power circuit operation mode                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| (17)V0 Voltage Regulator<br>Internal Resistor ratio<br>Set                                                                                                                                                                                                                                  | 0                 | 1               | 0                          | 0                               | 0             | 1                 | 0                     | 0                           | Res                               | istor R                            | atio                    | 20h<br>to<br>27h                                                               | Select internal resistor ratio Rb/Ra<br>mode                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| (18)Electronic Volume<br>mode Set                                                                                                                                                                                                                                                           | 0                 | 1               | 0                          | 1                               | 0             | 0                 | 0                     | 0                           | 0                                 | 0                                  | 1                       | 81h                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Electronic Volume<br>Register Set                                                                                                                                                                                                                                                           | 0                 | 1               | 0                          | *                               | *             |                   | Electr                | onic C                      | ontrol                            | Value                              |                         | XX                                                                             | Sets the V0 output voltage electronic volume register                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| (19)Set Static indicator<br>ON/OFF                                                                                                                                                                                                                                                          | 0                 | 1               | 0                          | 1                               | 0             | 1                 | 0                     | 1                           | 1                                 | 0                                  | 0                       |                                                                                | Sets static indicator ON/OFF<br>0: OFF, 1: ON                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Set Static Indicator<br>Register                                                                                                                                                                                                                                                            | 0                 | 1               | 0                          | *                               | *             | *                 | *                     | *                           | *                                 | Мо                                 | de                      | XX                                                                             | Sets the flash mode                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| (20)Power Save                                                                                                                                                                                                                                                                              | 0                 | 1               | 0                          | •                               | -             | -                 | -                     | -                           | -                                 | -                                  | -                       | -                                                                              | Compound command of Display<br>OFF and Entire Display ON                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| (21)NOP                                                                                                                                                                                                                                                                                     | 0                 | 1               | 0                          | 1                               | 1             | 1                 | 0                     | 0                           | 0                                 | 1                                  | 1                       | E3h                                                                            | Command for non-operation                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                                                                                                                                                                                                                                                                                             |                   |                 |                            |                                 |               |                   |                       | Code                        |                                   |                                    |                         |                                                                                | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Command                                                                                                                                                                                                                                                                                     | ΔΩ                | /RD             | /\/R                       |                                 |               |                   |                       |                             |                                   |                                    |                         |                                                                                | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Command                                                                                                                                                                                                                                                                                     | A0                | /RD             | /WR                        | D7                              | D6            | D5                | D4                    | D3                          | D2                                | D1                                 | D0                      | Hex                                                                            | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Command (22)Oscillation Frequency Select                                                                                                                                                                                                                                                    | <b>A0</b>         | /RD             | /WR<br>0                   | D7                              | D6            | D5                |                       |                             | _                                 | D1<br>0                            | 0<br>1                  |                                                                                | Function Select the oscillation frequency                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| (22)Oscillation Frequency                                                                                                                                                                                                                                                                   |                   |                 |                            |                                 |               |                   | D4                    | D3                          | D2                                |                                    | 0                       | E4h<br>E5h<br>82h                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| (22)Oscillation Frequency<br>Select<br>(23)Partial Display mode                                                                                                                                                                                                                             | 0                 | 1               | 0                          | 1                               | 1             | 1                 | D4<br>0               | D3                          | 1<br>0                            | 0                                  | 0 1 0 1                 | E4h<br>E5h<br>82h<br>83h<br>30h                                                | Select the oscillation frequency  Enter/Release the partial display                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| (22)Oscillation Frequency<br>Select<br>(23)Partial Display mode<br>Set                                                                                                                                                                                                                      | 0                 | 1               | 0                          | 1                               | 1 0           | 1 0               | 0<br>0                | D3<br>0                     | 1<br>0<br>Dt                      | 0                                  | 0<br>1<br>0<br>1        | E4h<br>E5h<br>82h<br>83h<br>30h<br>37h<br>38h                                  | Select the oscillation frequency  Enter/Release the partial display mode  Sets the LCD duty ratio for partial                                                                                                                                                                                                                                                                                                                                                                 |  |

| (22)Oscillation Frequency<br>Select<br>(23)Partial Display mode<br>Set<br>(24)Partial Display Duty Set                                                                                                                                                                                      | 0 0               | 1 1 1           | 0 0                        | 1 1 0                           | 1 0 0         | 1 0 1             | D4<br>0<br>0          | D3 0 0 0                    | 1<br>0<br>Dt                      | 0<br>1<br>uty Rat                  | 0<br>1<br>0<br>1        | E4h<br>E5h<br>82h<br>83h<br>30h<br>37h<br>38h                                  | Select the oscillation frequency  Enter/Release the partial display mode  Sets the LCD duty ratio for partial display mode  Sets the LCD bias ratio for partial                                                                                                                                                                                                                                                                                                               |  |

| (22)Oscillation Frequency<br>Select<br>(23)Partial Display mode<br>Set<br>(24)Partial Display Duty Set<br>(25)Partial Display Bias Set                                                                                                                                                      | 0 0 0             | 1 1 1 1         | 0 0 0                      | 1 1 0 0                         | 1 0 0         | 1 0 1             | D4 0 0 1 1 1          | D3 0 0 0 1 0 0              | 1<br>0<br>Du                      | 0<br>1<br>uty Ratas Rat            | 0<br>1<br>0<br>1<br>tio | E4h<br>E5h<br>82h<br>83h<br>30h<br>37h<br>38h<br>3Fh                           | Select the oscillation frequency  Enter/Release the partial display mode  Sets the LCD duty ratio for partial display mode  Sets the LCD bias ratio for partial display mode                                                                                                                                                                                                                                                                                                  |  |

| (22)Oscillation Frequency<br>Select<br>(23)Partial Display mode<br>Set<br>(24)Partial Display Duty Set<br>(25)Partial Display Bias Set<br>(26)Partial Start Line Set                                                                                                                        | 0 0 0 0           | 1 1 1 1 1       | 0 0 0 0                    | 1 0 0 1                         | 1 0 0 0 1     | 1 0 1             | D4 0 0 1 1 1          | D3 0 0 0 1 0 0              | D2 1 0 D0 Bi                      | 0<br>1<br>uty Ratas Rat            | 0<br>1<br>0<br>1<br>tio | E4h<br>E5h<br>82h<br>83h<br>30h<br>37h<br>38h<br>3Fh<br>D3h                    | Select the oscillation frequency  Enter/Release the partial display mode  Sets the LCD duty ratio for partial display mode  Sets the LCD bias ratio for partial display mode  Enter Partial Start Line Set  Sets the LCD Number of partial                                                                                                                                                                                                                                    |  |

| (22)Oscillation Frequency<br>Select<br>(23)Partial Display mode<br>Set<br>(24)Partial Display Duty Set<br>(25)Partial Display Bias Set<br>(26)Partial Start Line Set<br>Partial Start Line Set                                                                                              | 0 0 0 0 0         | 1 1 1 1 1       | 0 0 0 0 0                  | 1 0 0 1 1                       | 1 0 0 0 1 1   | 1 0 1 1 0         | D4 0 0 1 1 1 Pa       | D3 0 0 1 0 artial S         | D2 1 0 D0 Bi 0                    | 0 1 uty Rat as Rat 1 ne            | 0<br>1<br>0<br>1<br>tio | E4h<br>E5h<br>82h<br>83h<br>30h<br>37h<br>38h<br>3Fh<br>D3h<br>XX              | Select the oscillation frequency  Enter/Release the partial display mode  Sets the LCD duty ratio for partial display mode  Sets the LCD bias ratio for partial display mode  Enter Partial Start Line Set  Sets the LCD Number of partial display start line                                                                                                                                                                                                                 |  |

| (22)Oscillation Frequency Select (23)Partial Display mode Set (24)Partial Display Duty Set (25)Partial Display Bias Set (26)Partial Start Line Set Partial Start Line Set (27)N-Line Inversion Set Number of Line Set                                                                       | 0 0 0 0 0 0       | 1 1 1 1 1 1     | 0 0 0 0 0 0                | 1<br>1<br>0<br>0<br>1<br>1      | 1 0 0 0 1 1 0 | 1 0 1 1 0 0       | D4 0 0 1 1 1 Pa       | D3 0 0 1 0 artial S         | D2 1 0 D0 Bi 0 Start Li           | 0 1 uty Rat as Rat 1 ne            | 0<br>1<br>0<br>1<br>tio | E4h<br>E5h<br>82h<br>83h<br>30h<br>37h<br>38h<br>3Fh<br>D3h<br>XX              | Select the oscillation frequency  Enter/Release the partial display mode  Sets the LCD duty ratio for partial display mode  Sets the LCD bias ratio for partial display mode  Enter Partial Start Line Set  Sets the LCD Number of partial display start line  Enter N-Line inversion  Sets the number of line used for                                                                                                                                                       |  |

| (22)Oscillation Frequency Select (23)Partial Display mode Set (24)Partial Display Duty Set (25)Partial Display Bias Set (26)Partial Start Line Set Partial Start Line Set (27)N-Line Inversion Set Number of Line Set                                                                       | 0 0 0 0 0 0 0     | 1 1 1 1 1 1     | 0 0 0 0 0 0 0              | 1 0 0 1 1 1 1 *                 | 1 0 0 1 1 0 * | 1 0 1 1 0 0 *     | D4 0 0 1 1 1 Pa       | D3 0 0 1 0 artial S Num     | D2 1 0 D0 Bi 0 start Li 1         | 0 1 1 as Rate 1 ne 0 Line          | 0<br>1<br>0<br>1<br>tio | E4h<br>E5h<br>82h<br>83h<br>30h<br>37h<br>38h<br>3Fh<br>D3h<br>XX<br>85h<br>XX | Select the oscillation frequency  Enter/Release the partial display mode  Sets the LCD duty ratio for partial display mode  Sets the LCD bias ratio for partial display mode  Enter Partial Start Line Set  Sets the LCD Number of partial display start line Enter N-Line inversion  Sets the number of line used for N-Line inversion                                                                                                                                       |  |

| (22)Oscillation Frequency Select (23)Partial Display mode Set (24)Partial Display Duty Set (25)Partial Display Bias Set (26)Partial Start Line Set Partial Start Line Set (27)N-Line Inversion Set Number of Line Set                                                                       | 0 0 0 0 0 0 0 0   | 1 1 1 1 1 1 1 1 | 0 0 0 0 0 0 0 0            | 1<br>0<br>0<br>1<br>1<br>1<br>* | 1 0 0 1 1 0 * | 1 0 1 1 0 0 *     | D4 0 0 1 1 1 Pa       | D3 0 0 1 0 artial S Num 0 0 | D2 1 0 D0 Bi 0 Start Li 1 sber of | 0 1 aty Rate as Rate 1 ne 0 Line 0 | 0<br>1<br>0<br>1<br>tio | E4h E5h 82h 83h 30h 37h 38h 3Fh D3h XX 85h XX 84h E6h                          | Select the oscillation frequency  Enter/Release the partial display mode  Sets the LCD duty ratio for partial display mode  Sets the LCD bias ratio for partial display mode  Sets the LCD bias ratio for partial display mode  Enter Partial Start Line Set  Sets the LCD Number of partial display start line  Enter N-Line inversion  Sets the number of line used for N-Line inversion  Exit N-Line Inversion                                                             |  |

| (22)Oscillation Frequency Select (23)Partial Display mode Set (24)Partial Display Duty Set (25)Partial Display Bias Set (26)Partial Start Line Set Partial Start Line Set (27)N-Line Inversion Set Number of Line Set (28)N-Line Inversion Release (29)DC/DC Clock Set DC/DC Clock Division | 0 0 0 0 0 0 0 0 0 | 1 1 1 1 1 1 1 1 | 0<br>0<br>0<br>0<br>0<br>0 | 1<br>0<br>0<br>1<br>1<br>1<br>* | 1 0 0 1       | 1 0 1 1 0 0 * 0 1 | D4 0 0 1 1 1 Pa 0 0 0 | D3 0 0 1 0 artial S Num 0 0 | D2 1 0 D0 Bi 0 Start Li 1 sber of | 0 1 aty Rate as Rate 1 ne 0 Line 0 | 0<br>1<br>0<br>1<br>tio | E4h E5h 82h 83h 30h 37h 38h 3Fh D3h XX 85h XX 84h E6h XX                       | Select the oscillation frequency  Enter/Release the partial display mode  Sets the LCD duty ratio for partial display mode  Sets the LCD bias ratio for partial display mode  Sets the LCD bias ratio for partial display mode  Enter Partial Start Line Set  Sets the LCD Number of partial display start line  Enter N-Line inversion  Sets the number of line used for N-Line inversion  Exit N-Line Inversion  Set DC/DC Clock Frequency  Set the Division of DC/DC Clock |  |

Note: Do not use any other command, or system malfunction may result.

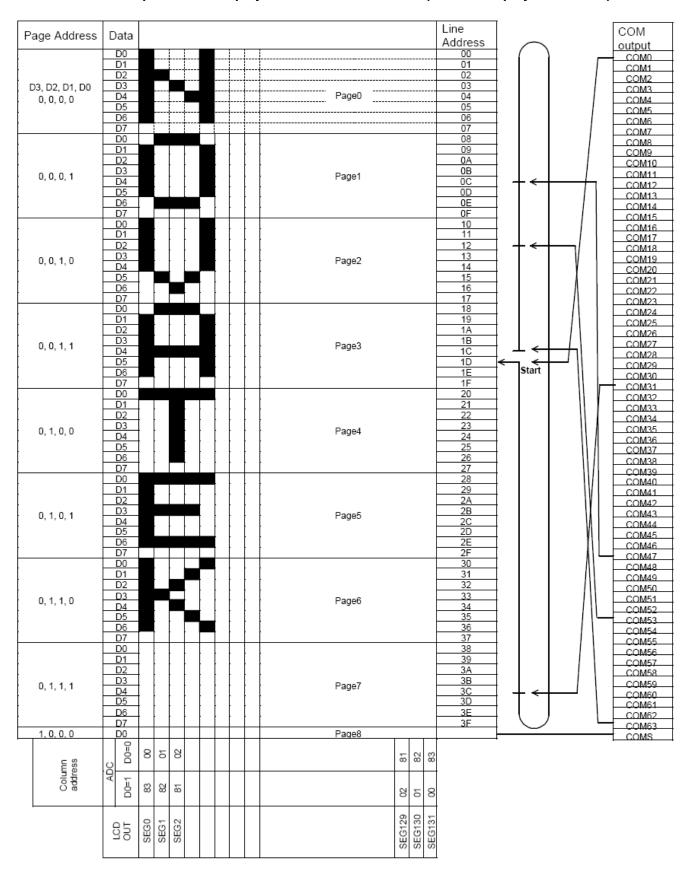

## DISPLAY DATA RAM:

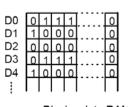

The display data RAM is RAM that stores the dot data for the display. It has a 65 (8 page \* 8 bit+1)\*132 bit structure. It is possible to access the desired bit by specifying the page address and the column address. Because, as is shown in Figure 3, the D7 to D0 display data from the MPU corresponds to the liquid crystal display common direction, there are few constraints at the time of display common direction, and there are few constraints at the time of display data transfer when multiple NT7538 chips are used, thus display structures can be created easily with a high degree of freedom.

Moreover, reading from and writing to the display RAM from the MPU side is performed through the I/O buffer, which is an independent operation from signal reading for the liquid crystal driver. Consequently, even if the display data RAM is accessed asynchronously during the liquid crystal display, it will not cause adverse effects on the display (such as flickering). Figure 3

COM0 [ COM1 COM2 COM3 COM4

Display data RAM

Display on LCD

#### The Page Address Circuit

As shown in Figure 4, page address of the display data RAM is specified through the Page Address Set Command. The page address must be specified again when changing pages to perform access. Page address8 (D3, D2, D1, D0 = 1, 0, 0, 0, 0) is the page for the RAM region used; only display data D0 is used.

#### The Column Address

As shown in Figure 4, the display data RAM column address is specified by the Column Address Set command. The specified column address is incremented (+1) with each display data read / write command. This allows the MPU display data to be accessed continuously. Moreover, the incrimination of column addresses stops with 83H, because the column address is independent of the page address.

Thus, when moving, for example, from page 0 column 83H to page 1 column 00H, it is necessary to specify both the page address and the column address.

Furthermore, as is shown in Table 4, the ADC command (segment driver direction select command) can be used to reverse the relationship between the display data RAM column address and the segment output. Because of this, the constraints on the IC layout when the LCD module is assembled can be minimized.

|            | 1 0             | ible 4         |                |

|------------|-----------------|----------------|----------------|

| SEG Output | SEG0            |                | SEG131         |

| ADC "0"    | 0 (H)→          | Column Address | →83 (H)        |

| (ADC) "1"  | 83 (H) <b>←</b> | Column Address | <b>←</b> 0 (H) |

#### The Line Address Circuit

The line address circuit, as shown in Table 4, specifies the line address relating to the COM output when the contents of the display data RAM are displayed. Using the display start line address set command, what is normally the top line of the display can be specified. This is the COM0 output when the common output mode is normal and the COM63 output for NT7538, when the common output mode is reversed. The display area is a 65-line area for the NT7538 from the display start line address. If the line addresses are changed dynamically using the display start line address set command, screen scrolling, page swapping, etc. can be performed.

#### The Display Data Latch Circuit

The display data latch circuit is a latch that temporarily stores the display data that is output to the liquid crystal driver circuit from the display data RAM. Because the display normal/reverse status, display ON/OFF status, and display all points ON/OFF commands control only the data within the latch, they do not change the data within the display data RAM itself.

#### **The Oscillator Circuit**

This is a CR-type oscillator that produces the display clock. The oscillator circuit is only enabled when M/S = "H" and CLS = "H". When CLS = "L" the oscillation stops, and the display clock is input through the CL terminal.

#### Relationship between display data RAM and address. (if initial display line is 1DH)

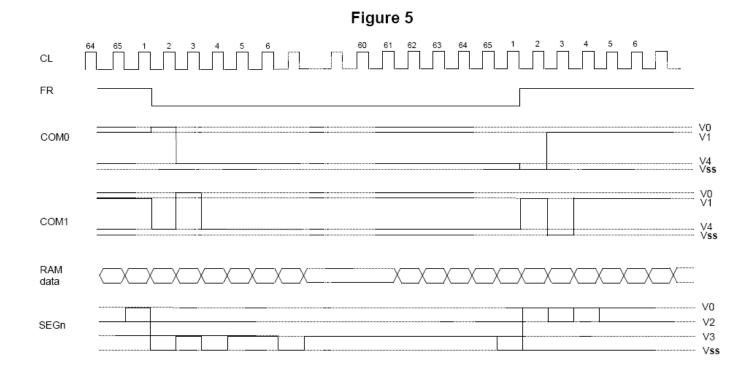

#### **Display Timing Generator Circuit**

The display timing generator circuit generates the timing signal to the line address circuit and the display data latch circuit using the display clock. The display data is latched into the display data latch circuit synchronized with the display clock, and is output to the data driver output terminal. Reading to the display data liquid crystal driver circuits is completely independent of access to the display data RAM by the MPU. Consequently, even if the display data RAM is accessed asynchronously during liquid crystal display, there is absolutely no adverse effect (such as flickering) on the display.

Moreover, the display timing generator circuit generates the common timing and the liquid crystal alternating current signal (FR) from the display clock. It generates a drive waveform using a 2 frames alternating current drive method, as shown in Figure 5, for the liquid crystal drive circuit.

When multiple NT7538 chips are used, the slave chip must be supplied with the display timing signals (FR, CL, /DOF) from the master chip. Table 5 shows the status of the FR, CL, and /DOF signals.

Operating Mode FR CL /DOF Master The internal display oscillator is enabled (CLS = "H") Output Output Output Output The internal display oscillator is disabled (CLS = "L") (M/S = "H")Output Input The internal display oscillator is disabled (CLS = "H") Slave Input Input Input (M/S = "L")The internal display oscillator is disabled (CLS = "L") Input Input Input

Table 5

Table 6 shows the relationship between oscillation frequency and frame frequency. fOSC can be selected as 31.4K or 26.3KHz by using Oscilliation Frequency Select command.

Table 6

| Duty | Item                           | fCL                | fFR          |

|------|--------------------------------|--------------------|--------------|

| 1/65 | On-chip oscillator is used     | fOSC/6             | fCL/(2 x 65) |

| 1/65 | On-chip oscillator is not used | External input fCL | fCL/(2 x 65) |

| 1/49 | On-chip oscillator is used     | fOSC/8             | fCL/(2 x 49) |

| 1/49 | On-chip oscillator is not used | External input fCL | fCL/(2 x 49) |

| 1/33 | On-chip oscillator is used     | fOSC/12            | fCL/(2 x 33) |

| 1/33 | On-chip oscillator is not used | External input fCL | fCL/(2 x 33) |

| 1/17 | On-chip oscillator is used     | fOSC/22            | fCL/(2 x 17) |

| 1/17 | On-chip oscillator is not used | External input fCL | fCL/(2 x 17) |

| 1/9  | On-chip oscillator is used     | fOSC/44            | fCL/(2 x 9)  |

| 1/9  | On-chip oscillator is not used | External input fCL | fCL/(2 x 9)  |

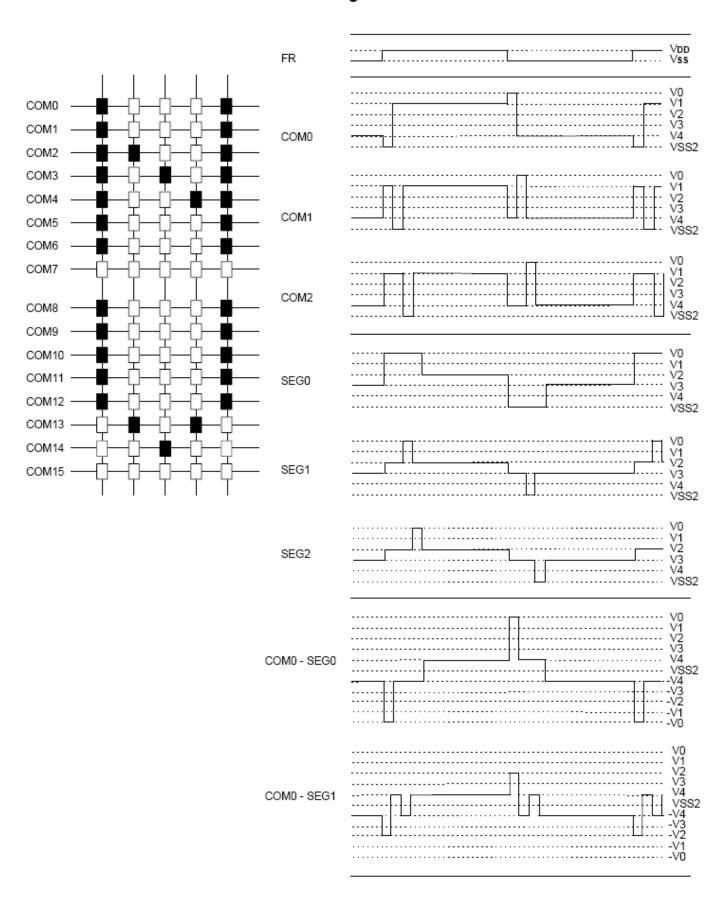

#### **Common Output Control Circuit**

This circuit controls the relationship between the number of common output and specified duty ratio. Common output mode select instruction specifies the scanning direction of the common output pads.

Table 7

|             |                  | Common output pads |                |                |                |                |                |           |        |  |

|-------------|------------------|--------------------|----------------|----------------|----------------|----------------|----------------|-----------|--------|--|

| Duty Status |                  | COM<br>[0-15]      | COM<br>[16-23] | COM<br>[24-26] | COM<br>[27-36] | COM<br>[40-47] | COM<br>[48-63] | COMS      |        |  |

| 1/33        | Normal           | COM[0-15]          |                | NC COM[16-31]  |                |                |                |           | COMS   |  |